Product Summary

The LPC1766FBD100 is an ARM Cortex-M3 based microcontroller for embedded applications featuring a high level of integration and low power consumption. The LPC1766FBD100 is a next generation core that offers system enhancements such as enhanced debug features and a higher level of support block integration. The LPC1766FBD100 operates at CPU frequencies of up to 100 MHz. The ARM Cortex-M3 CPU incorporates a 3-stage pipeline and uses a Harvard architecture with separate local instruction and data buses as well as a third bus for peripherals. The ARM Cortex-M3 CPU also includes an internal prefetch unit that supports speculative branching. The applications of the LPC1766FBD100 include eMetering, Alarm systems, Lighting, White goods, Industrial networking, Motor control.

Parametrics

LPC1766FBD100 absolute maximum ratings: (1)supply voltage (3.3 V), core and external rail, VDD(3V3): 2.4 to 3.6 V; (2)regulator supply voltage (3.3 V), VDD(REG)(3V3): 2.4 to 3.6 V; (3)analog 3.3 V pad supply voltage, VDDA: -0.5 to +4.6 V; (4)input voltage on pin VBAT for the RTC, Vi(VBAT): -0.5 to +4.6 V; (5)input voltage on pin VREFP, Vi(VREFP): -0.5 to +4.6 V; (6)analog input voltage, on ADC related pins, VIA: -0.5 to +5.1 V; (7)input voltage, VI: -0.5 to +5.5 V; other I/O pins, VI: -0.5 VDD(3V3) to +0.5V; (8)supply current, per supply pin, IDD: -100 mA; (9)ground current, per ground pin, ISS: -100 mA; (10)I/O latch-up current, Ilatch: 100 mA; (11)Tstg storage temperature [5] .65 +150℃; (12)total power dissipation (per package), Ptot(pack): 1.5 W; (13)electrostatic discharge voltage, VESD: -4000 to +4000 V.

Features

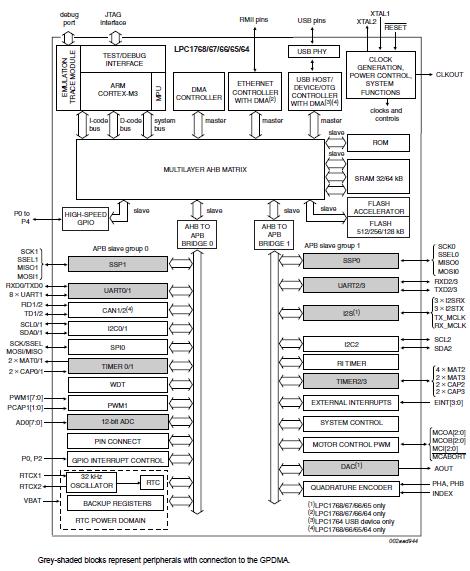

LPC1766FBD100 features: (1)ARM Cortex-M3 processor, running at frequencies of up to 100MHz. A Memory Protection Unit (MPU) supporting eight regions is included; (2)ARM Cortex-M3 built-in Nested Vectored Interrupt Controller(NVIC); (3)Up to 512 kB on-chip flash programming memory. Enhanced flash memory accelerator enables high-speed 100 MHz operation with zero wait states; (4)In-System Programming (ISP) and In-Application Programming (IAP) via on-chip bootloader software; (5)Eight channel General Purpose DMA controller (GPDMA) on the AHB multilayer matrix that can be used with SSP, I2S-bus, UART, Analog-to-Digital and Digital-to-Analog converter peripherals, timer match signals, and for memory-to-memory transfers; (6)Multilayer AHB matrix interconnect provides a separate bus for each AHB master. AHB masters include the CPU, General Purpose DMA controller, Ethernet MAC, and the USB interface. This interconnect provides communication with no arbitration delays; (7)Split APB bus allows high throughput with few stalls between the CPU and DMA; (8)Standard JTAG test/debug interface for compatibility with existing tools. Serial Wire Debug and Serial Wire Trace Port options.; (9)Emulation trace module enables non-intrusive, high-speed real-time tracing of instruction execution; (10)Integrated PMU (Power Management Unit) automatically adjusts internal regulators to minimize power consumption during Sleep, Deep sleep, Power-down, and Deep power-down modes; (11)Four reduced power modes: Sleep, Deep-sleep, Power-down, and Deep power-down; (12)Single 3.3 V power supply (2.4 V to 3.6 V); (13)Four external interrupt inputs configurable as edge/level sensitive. All pins on Port 0; (14)and Port 2 can be used as edge sensitive interrupt sources; (15)Non-maskable Interrupt (NMI) input; (16)Clock output function that can reflect the main oscillator clock, IRC clock, RTC clock, CPU clock, and the USB clock; (17)The Wakeup Interrupt Controller (WIC) allows the CPU to automatically wake up from any priority interrupt that can occur while the clocks are stopped in deep sleep, Power-down, and Deep power-down modes; (18)Processor wake-up from Power-down mode via any interrupt able to operate during Power-down mode (includes external interrupts, RTC interrupt, USB activity, Ethernet wake-up interrupt, CAN bus activity, Port 0/2 pin interrupt, and NMI); (19)Brownout detect with separate threshold for interrupt and forced reset; (20)Power-On Reset (POR); (21)Crystal oscillator with an operating range of 1 MHz to 25 MHz; (22)4 MHz internal RC oscillator trimmed to 1 % accuracy that can optionally be used as a system clock; (23)PLL allows CPU operation up to the maximum CPU rate without the need for a high-frequency crystal. May be run from the main oscillator, the internal RC oscillator, or the RTC oscillator; (24)USB PLL for added flexibility; (25)Code Read Protection (CRP) with different security levels; (26)Available as 100-pin LQFP package (14 × 14 × 1.4 mm).

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

LPC1766FBD100,551 |

NXP Semiconductors |

ARM Microcontrollers (MCU) ARM Cortex M3 Micro Controller |

Data Sheet |

|

|

||||||||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|

LPC10065ATED100K |

KOA Speer |

Common Mode Inductors (Chokes) 10uH 10% |

Data Sheet |

|

|

||||||||||||

|

LPC10065ATED101K |

KOA Speer |

Common Mode Inductors (Chokes) 100uH 10% |

Data Sheet |

|

|

||||||||||||

|

LPC10065ATED102K |

KOA Speer |

Common Mode Inductors (Chokes) 1000uH 10% |

Data Sheet |

|

|

||||||||||||

|

LPC10065ATED150K |

KOA Speer |

Common Mode Inductors (Chokes) 15uH 10% |

Data Sheet |

|

|

||||||||||||

|

LPC10065ATED151K |

KOA Speer |

Common Mode Inductors (Chokes) 150uH 10% |

Data Sheet |

|

|

||||||||||||

|

LPC10065ATED152K |

KOA Speer |

Common Mode Inductors (Chokes) 1500uH 10% |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))